Virtex 5 Block Diagram - Jika kamu sedang mencari artikel Virtex 5 Block Diagram terbaru, berarti kamu telah berada di website yang benar. Setiap artikel dibahas secara tuntas dengan penyajian bahasa yang ringan dimengerti bagi orang awam sekalipun. itulah sebabnya web ini banyak diminati para blogger dan pembaca online. Yuk langsung saja kita simak ulasan Virtex 5 Block Diagram berikut ini.

Virtex 5 Block Diagram. Typical CRC Block Application DATA_USd-10 REM_USp0 SOF_N_US EOF_N. Updated timing diagrams and descriptions for Figure 12-13 Figure 12-14 and Figure 12-17. The configuration connections from the SPI serial flash to the FPGA are highlighted in this diagram. The Virtex-5 SYSMON hard macro function block diagram as shown in Figure 1 is built around a 10-bit 200-kSPS kilo-Samples Per Second Analog-to-Digital Converter ADC with a resolution of 1 mV. Virtex-5 FPGA Aurora 64B66B v13.

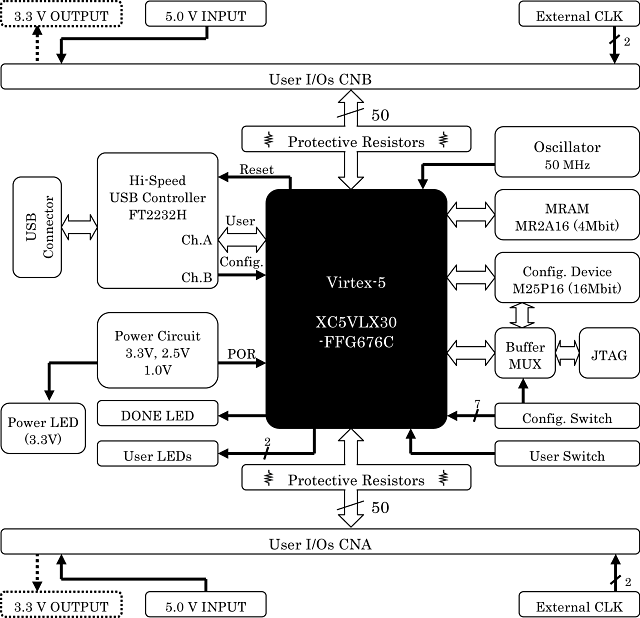

North Star Generator Wiring Diagrams Figure 2 is a high-level block diagram of the Virtex-5 FPGA QDR II memory reference design showing both the external connections to the QDR II memory device and the internal FPGA fabric interface for initiating ReadWrite commands. For information on the. Virtex-5 FPGA ML561 Development Board Block Diagram. The C and C pins of the QDR II memory device are tied High in Figure 2. The configuration connections from the SPI serial flash to the FPGA are highlighted in this diagram. 1 2 x7r 16v 001uf c11 2 1 c88 001uf 16v x7r 2 1 c161 100nf 16v.

Virtex 5 Block Diagram It is far more helpful as a reference guide if anyone wants to know about the homes electrical system.

Caravan Sway Bar Diagram 17 art pn 0531589-01 fab pn 1280401-01 sch pn 0381320-01 schemrohs compliant virtex 5 ff324 daughter 1280401 01 b. See the Virtex-5 FPGA Virtex-5 FPGA. Virtex 5 ff324 daughter 1280401 art pn 0531589-01 fab pn 1280401-01 sch pn 0381320-01 01 b dl. Virtex-5 FPGA RocketIO GTX Transceiver User Guide This guide describes the RocketIO GTX transc eivers available in the Virtex-5 TXT and FXT platforms. Provides the pinout diagrams for the Virtex-5QV FPGA in the CF1752 package. Sheetblock 22 xilinx virtex-5 sx50t configuration 22b virtex-5 sx50t cclk 22c system monitor precision reference 22d virtex-5 sx50t fpga configuration mode 22e virtex-5 sx50t fpga spi mode 23 xilinx virtex-5 sx50t io 23b ddr2qdr-ii reference.

5b depicts a Virtex-5 DSP block called the DSP48E.

Modern House Wiring Diagram Complete and up-to-date documentation of the Virtex-5 family of FPGAs is. DUC and DDC design files for 4-carrier GSM targeting Virtex-5 FPGAs Application Note. Virtex-5 FPGA Integrated Endpoint Block User Guide for PCI Express Designs This guide describes the integrated Endpoint blocks in the Virtex-5 LXT SXT TXT and FXT platforms used for PCI Express designs. Added Block RAM SSR in Regi ster Mode page 126 and FIFO Architecture. 25 art pn 0531590-01 fab pn 1280402-01 sch pn 0381231-01 schemrohs compliant virtex 5 ff1153 daughter 1280402 01 b.

128 MB 32M x 32 bits at 200 MHz clock speed.

Touch Light Sensor Wiring Diagram Es sentially the Virtex-5 family interconnect. Three XC5VLX50T-FFG1136 FPGAs see DS100 Virtex-5 Family Overview DDR400 components. Es sentially the Virtex-5 family interconnect. See the Virtex-5 FPGA Virtex-5 FPGA. Provides the pinout diagrams for the Virtex-5QV FPGA in the CF1752 package. The kit delivers a stable platform to develop and test designs targeted to the advanced Xilinx FPGA.

A high-level block diagram of the Virtex-5 LXTSXT PCI Express board is shown below followed by a.

Sony Cdx Gt330 Wiring Diagram Sheetblock 22 xilinx virtex-5 sx50t configuration 22b virtex-5 sx50t cclk 22c system monitor precision reference 22d virtex-5 sx50t fpga configuration mode 22e virtex-5 sx50t fpga spi mode 23 xilinx virtex-5 sx50t io 23b ddr2qdr-ii reference. See the Virtex-5 FPGA Virtex-5 FPGA. The configuration connections from the SPI serial flash to the FPGA are highlighted in this diagram. A detailed SPI configuration setup is shown in Figure 2 page 5 where the Virtex-5 FPGA is the master and the Numonyx SPI serial flash is the slave. For detailed information and updates about the Virtex-5 FPGA CRC Wizard core see the following documents located at Xilinx IP Center Page.

Virtex-5 Family XAPP1113 v10 November 21 2008 Designing Efficient Digital Up and Down Converters for Narrowband Systems Author.

1996 Infiniti I30 Wiring Diagram The configuration connections from the SPI serial flash to the FPGA are highlighted in this diagram. See XAPP851 DDR SDRAM Controller Using Virtex-5. Using the second generation ASMBL Advanced Silicon Modular Block column-based architecture the Virtex-5 family contains four distinct platforms sub-families the most choice offered by any FPGA family. Virtex-5 FPGA CRC Wizard v13 Data Sheet Virtex-5 FPGA CRC Wizard Release Notes X-Ref Target - Figure 1-1 Figure 1-1. Sheetblock 22 xilinx virtex-5 sx50t configuration 22b virtex-5 sx50t cclk 22c system monitor precision reference 22d virtex-5 sx50t fpga configuration mode 22e virtex-5 sx50t fpga spi mode 23 xilinx virtex-5 sx50t io 23b ddr2qdr-ii reference. For detailed information and updates about the Virtex-5 FPGA CRC Wizard core see the following documents located at Xilinx IP Center Page.

Typical CRC Block Application DATA_USd-10 REM_USp0 SOF_N_US EOF_N.

Wiring Diagram De Taller Citroen C15 Block Diagram of a Virtex-5 6-Input LUT WP245_03_051006 LUT5 A1 A2 A3 A4 D A5 A6 A2 A3 A4 D D6 D5 A5 A6 A3 A4 A6 LUT6 LUT5. Virtex 5 Block Diagram It is far more helpful as a reference guide if anyone wants to know about the homes electrical system. Added Block RAM SSR in Regi ster Mode page 126 and FIFO Architecture. Using the second generation ASMBL Advanced Silicon Modular Block column-based architecture the Virtex-5 family contains four distinct platforms sub-families the most choice offered by any FPGA family. Virtex 5 ff324 daughter 1280401 art pn 0531589-01 fab pn 1280401-01 sch pn 0381320-01 01 b dl.

Virtex 5 Block Diagram It is far more helpful as a reference guide if anyone wants to know about the homes electrical system.

1998 Buick Skylark Engine Diagram Updated timing diagrams and descriptions for Figure 12-13 Figure 12-14 and Figure 12-17. Virtex 5 ff324 daughter 1280401 art pn 0531589-01 fab pn 1280401-01 sch pn 0381320-01 01 b dl. See the Virtex-5 FPGA Virtex-5 FPGA. Three XC5VLX50T-FFG1136 FPGAs see DS100 Virtex-5 Family Overview DDR400 components. Complete and up-to-date documentation of the Virtex-5 family of FPGAs is. Virtex-5 FPGA ML561 Development Board Block Diagram.

Virtex-5 FPGA ML561 Development Board Block Diagram.

Rs 485 2wire Diagram Figure 2 shows a block diagram of the implementation of the Aurora 64B66B core. The Virtex-5 FPGA ML561 Development Board includes the following major functional blocks. Multiple block RAMs are organized into columns on the Virtex-5 device and two adjacent block RAMs can be combined to implement deeper memories. Virtex-5 FPGA Aurora 64B66B v13. The line rate for Virtex-5 FPGA cores can be set from 150 Mbps to 625 Gbps using the CORE Generator software.

Added Block RAM SSR in Regi ster Mode page 126 and FIFO Architecture.

2008 Wilson Wiring Diagram Stephen Creaney and Igor Kostarnov R. Reading and writing from the block RAM is a synchronous operation. The major func-. Embedded Processor Block in Virtex-5 FPGAs Reference Guide This reference guide is a description of the embedded processor block available in the Virtex-5 FXT platform. The configuration connections from the SPI serial flash to the FPGA are highlighted in this diagram. See the Virtex-5 FPGA Virtex-5 FPGA.

Virtex-5 Family XAPP1113 v10 November 21 2008 Designing Efficient Digital Up and Down Converters for Narrowband Systems Author.

Pontiac G6 Fuse Box Diagram For information on the. Multiple block RAMs are organized into columns on the Virtex-5 device and two adjacent block RAMs can be combined to implement deeper memories. They also offer benefits in simplifying the use of clocking and physical IO resources. The line rate for Virtex-5 FPGA cores can be set from 150 Mbps to 625 Gbps using the CORE Generator software. Vcc33 vcco_0 vcc3_en vcc_tmp vcco_0.

Introduction to Virtex-5 11 Virtex-5 FPGA The Virtex-5 family provides the newest most powerful features in the FPGA market.

Trailer Wiring Diagram Saturn Vcc33 vcco_0 vcc3_en vcc_tmp vcco_0 vcc33 vcco_0. Each block RAM has independent write and read ports available. Virtex-5 FPGA CRC Wizard v13 Data Sheet Virtex-5 FPGA CRC Wizard Release Notes X-Ref Target - Figure 1-1 Figure 1-1. The Virtex-5 SYSMON hard macro function block diagram as shown in Figure 1 is built around a 10-bit 200-kSPS kilo-Samples Per Second Analog-to-Digital Converter ADC with a resolution of 1 mV. Introduction to Virtex-5 11 Virtex-5 FPGA The Virtex-5 family provides the newest most powerful features in the FPGA market. Figure 2 shows a block diagram of the implementation of the Aurora 64B66B core.

Complete and up-to-date documentation of the Virtex-5 family of FPGAs is.

S Video Cable Wiring Diagram Wrapper files enable you to easily set the parameters and interface only to those ports required for your application. Sheetblock 22 xilinx virtex-5 sx50t configuration 22b virtex-5 sx50t cclk 22c system monitor precision reference 22d virtex-5 sx50t fpga configuration mode 22e virtex-5 sx50t fpga spi mode 23 xilinx virtex-5 sx50t io 23b ddr2qdr-ii reference. Added Block RAM SSR in Regi ster Mode page 126 and FIFO Architecture. Its components are shown by the pictorial to be easily identifiable. A Top-Level View page 134.

Virtex-5 FPGA Aurora 64B66B v13.

Fuse Box Diagram For Rover 75 5b depicts a Virtex-5 DSP block called the DSP48E. The Virtex-5 FPGA ML561 Development Board includes the following major functional blocks. Revised Global Clock Buffers page 20 to clarify single-ended clock pins. 5b depicts a Virtex-5 DSP block called the DSP48E. Changed the P and N IO designations in Figure 1-19. Three XC5VLX50T-FFG1136 FPGAs see DS100 Virtex-5 Family Overview DDR400 components.

Revised Global Clock Buffers page 20 to clarify single-ended clock pins.

Frigidaire Electric Oven Wiring Diagram The Virtex-5 LXTSXT PCI Express Development Kit provides a complete hardware environment for designers to accelerate their time to market. Figure 3 Block diagram of the Virtex-5 Ethernet MAC wrappers The Ethernet MAC is a complex component with 162 ports and 79 parameters. Revised Global Clock Buffers page 20 to clarify single-ended clock pins. Using the second generation ASMBL Advanced Silicon Modular Block column-based architecture the Virtex-5 family contains four distinct platforms sub-families the most choice offered by any FPGA family. They also offer benefits in simplifying the use of clocking and physical IO resources.

Block Diagram of a Virtex-5 6-Input LUT WP245_03_051006 LUT5 A1 A2 A3 A4 D A5 A6 A2 A3 A4 D D6 D5 A5 A6 A3 A4 A6 LUT6 LUT5.

Kubota Rtv1140cpx Wiring Diagram Online Virtex-5 FPGA Integrated Endpoint Block User Guide for PCI Express Designs This guide describes the integrated Endpoint blocks in the Virtex-5 LXT SXT TXT and FXT platforms used for PCI Express designs. 5b depicts a Virtex-5 DSP block called the DSP48E. Virtex-5 FPGA ML561 Development Board Block Diagram. For detailed information and updates about the Virtex-5 FPGA CRC Wizard core see the following documents located at Xilinx IP Center Page. Introduction to Virtex-5 11 Virtex-5 FPGA The Virtex-5 family provides the newest most powerful features in the FPGA market. Virtex-5 FPGA Integrated Endpoint Block User Guide for PCI Express Designs This guide describes the integrated Endpoint blocks in the Virtex-5 LXT SXT TXT and FXT platforms used for PCI Express designs.

For information on the.

1993 Corolla Fuel Injector Wiring Diagram Figure 3 Block diagram of the Virtex-5 Ethernet MAC wrappers The Ethernet MAC is a complex component with 162 ports and 79 parameters. The configuration connections from the SPI serial flash to the FPGA are highlighted in this diagram. Virtex-5 FPGA ML561 Development Board Block Diagram. 25 art pn 0531590-01 fab pn 1280402-01 sch pn 0381231-01 schemrohs compliant virtex 5 ff1153 daughter 1280402 01 b. Vcc33 vcco_0 vcc3_en vcc_tmp vcco_0.

Situs ini adalah komunitas terbuka bagi pengguna untuk mencurahkan apa yang mereka cari di internet, semua konten atau gambar di situs web ini hanya untuk penggunaan pribadi, sangat dilarang untuk menggunakan artikel ini untuk tujuan komersial, jika Anda adalah penulisnya dan menemukan gambar ini dibagikan tanpa izin Anda, silakan ajukan laporan DMCA kepada Kami.

Jika Anda menemukan situs ini bagus, tolong dukung kami dengan membagikan postingan ini ke akun media sosial seperti Facebook, Instagram dan sebagainya atau bisa juga save halaman blog ini dengan judul Virtex 5 Block Diagram dengan menggunakan Ctrl + D untuk perangkat laptop dengan sistem operasi Windows atau Command + D untuk laptop dengan sistem operasi Apple. Jika Anda menggunakan smartphone, Anda juga dapat menggunakan menu laci dari browser yang Anda gunakan. Baik itu sistem operasi Windows, Mac, iOS, atau Android, Anda tetap dapat menandai situs web ini.